Le tecnologie avanzate di packaging dei chip integrati 3D (SoIC) di TSMC sono destinate a svilupparsi rapidamente. In una presentazione al recente simposio tecnologico dell'azienda, TSMC ha delineato una tabella di marcia che porterà la tecnologia dall'attuale intervallo di impatto di 9 µm fino a 3 µm entro il 2027, con lotti di matrici A16 e N2 raggruppati insieme.

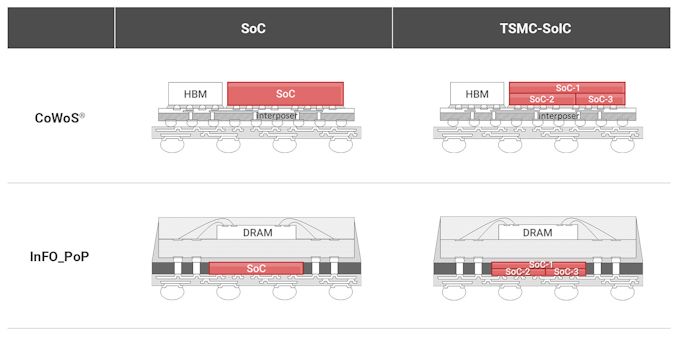

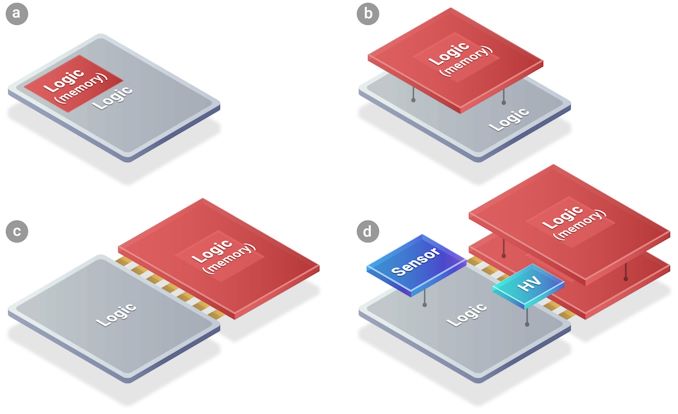

TSMC dispone di una serie di tecnologie di packaging avanzate, tra cui 2.5D CoWoS e 2.5D/3D InFO. Forse l'approccio più interessante (e complesso) è la tecnologia dei chip integrati 3D (SoIC), che è l'applicazione di TSMC dell'interconnessione dei chip ibridi. L'interconnessione ibrida consente di impilare due dispositivi logici di fascia alta direttamente uno sopra l'altro, consentendo connessioni molto dense (e molto brevi) tra i due chip, ed è rivolta principalmente a componenti ad alte prestazioni. Attualmente, SoIC-X (non-shock) viene utilizzato per applicazioni specifiche, come la tecnologia 3D V-cache di AMD per CPU, nonché i prodotti AI della serie Instinct MI300. Sebbene l'adozione di questa tecnologia sia in aumento, l'attuale generazione di tecnologia è limitata da limitazioni sulle dimensioni dello stampo e sui gradi di interconnessione.

Ma si prevede che queste restrizioni svaniranno rapidamente, se tutto andrà secondo i piani di TSMC. La tecnologia SoIC-X avanzerà rapidamente ed entro il 2027 sarà possibile assemblare un chip che accoppia un die superiore delle dimensioni di un reticolo realizzato sul chip A16 di punta di TSMC (classe 1,6 nm) su un die inferiore prodotto con N2 di TSMC (classe 2 nm). ). Questi stampi verranno a loro volta forniti utilizzando TSV con strato di silicio da 3 micrometri, tre volte la densità di volume dell'attuale strato di silicio da 9 micrometri. Interconnessioni così piccole consentirebbero complessivamente un numero molto maggiore di connessioni, aumentando notevolmente la densità di larghezza di banda (e quindi le prestazioni) del chip assemblato.

| Roadmap SoIC-X di TSMC Dati di TSMC (compilati da AnandTech) |

||||||||

| 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | |||

| Muori in alto | N7 | N5 | N4 | N4 | N2 | A16 | ||

| Il fondo muore | N7 | ≥N6 | ≥N5 | ≥N4 | ≥N3 | ≥N2 | ||

| Pitch Bond | 9 micron | 9 micron | 6 micron | 6 micron | 4,5 µm | 3 micron | ||

| misurazione* | reticolo 0,1 | reticolo 0,4 | Reticolo 0,8 | 1 reticolo | 1 reticolo | 1 reticolo | ||

*TSMC considera che la dimensione del reticolo sia di circa 830 mm2.

Le tecnologie di interconnessione ibride avanzate hanno lo scopo di consentire ai grandi clienti HPC di TSMC – AMD, Broadcom, Intel, NVIDIA e simili – di costruire architetture di processori grandi, altamente dettagliate e dense per applicazioni impegnative, dove la distanza tra i die è fondamentale, così come lo è spazio Piano lordo utilizzato. Nel frattempo, per le applicazioni in cui sono importanti solo le prestazioni, sarà possibile posizionare più pacchetti SoIC-X sul broker CoWoS per ottenere prestazioni migliori con un consumo energetico inferiore.

Oltre a sviluppare la tecnologia di packaging SoIC-X destinata ai dispositivi che richiedono prestazioni estreme, TSMC lancerà nel prossimo futuro anche il processo di packaging SoIC-P. Il SoIC-P è progettato per applicazioni con prestazioni a basso costo che richiedono comunque lo stacking 3D, ma non necessitano delle prestazioni e della complessità aggiuntive fornite dalle connessioni TSV rame-rame. Questa tecnologia di packaging consentirà a un'ampia gamma di aziende di trarre vantaggio dal SoIC e, sebbene TSMC non possa parlare dei piani dei suoi clienti, una versione più economica della tecnologia potrebbe renderla più accessibile per le applicazioni consumer più attente ai costi.

Secondo i piani attuali di TSMC, entro il 2025 l'azienda introdurrà una tecnologia SoIC-P faccia a retro (F2B) in grado di accoppiare un die superiore N3 con reticolo di 0,2 (classe 3 nm) con un die inferiore N4 (classe 4 nm) , che verrà collegato utilizzando microbump di passo 25μm(μbumps). Nel 2027, TSMC introdurrà la tecnologia SoIC-P face-to-face (F2F), che sarà in grado di posizionare il die superiore N2 sul die inferiore N3 a una distanza di 16 µm.

| Roadmap SoIC-P di TSMC Dati di TSMC (compilati da AnandTech) |

||||

| 2025 | 2027 | |||

| Muori in alto | N3 | N2 | ||

| Il fondo muore | ≥N4 | ≥N3 | ||

| Pitch Bond | 25 micron | 16 micron | ||

| misurazione* | reticolo 0,2 | reticolo 0,4 | ||

| Orientamento del modello | Faccia a schiena | faccia a faccia | ||

| Tempo di qualificazione | SoC mobile del quarto trimestre del 2024 | Secondo trimestre del 2026 per il calcolo ad alte prestazioni | ||

*TSMC considera che la dimensione del reticolo sia di circa 830 mm2

C'è ancora molto lavoro da fare per rendere i SoIC più popolari e accessibili tra gli sviluppatori di chip, incluso continuare a migliorare le loro interfacce senza uscita. Ma TSMC sembra essere molto ottimista riguardo all’adozione dei SoIC da parte del settore e prevede di rilasciare circa 30 progetti SoIC entro il 2026-2027.

“Esploratore. Scrittore appassionato. Appassionato di Twitter. Organizzatore. Amico degli animali ovunque.”